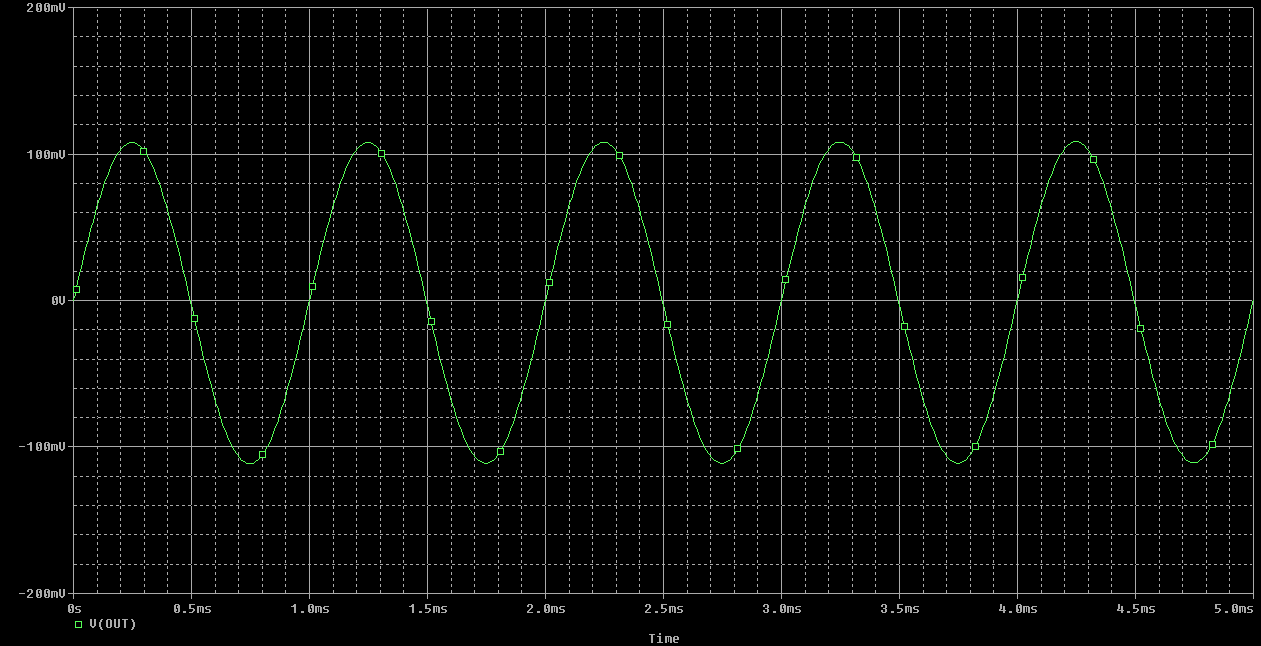

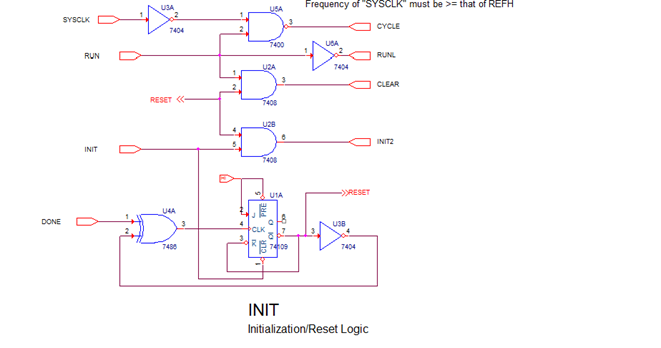

Simulate the complete counter circuit by OrCAD and PSPICE. The single-digit decade counter should be built by a cascaded synchronous binary counter (74LS163) and other basic logic gates.

5us SLK DELAY = STARTVAL = 0 OPPVAL = 1 Part List: DiClock FileStim1 FileStim 16 FileStim2 FileStim32 Filostim4 File Stim8 IAC Libraries: abc Design Cache EVAL SOURCE 2Ĥ504189) 0.800 MINI 9.10 140X551) 1102953 31.10.043) 0.32 & 56.3351 0.281610) 3.00 120/MIN E5-A32xRD 1,6 D DP BS-C323RD 1,6 A B C D E F GDP TBCDEFGDP 10 5 4 13Ī) Design a single-digit decade counter that counts from 0 to 9 and repeats. Transcribed image text: Part 2 DigClock 2 OFFTIME =. Show transcribed image text Expert Answer Draw the circuitĬonnection of the decade counter in (a) and theĭecoder to display the count value on the 7-segment LED display.Ĭonfiguration is needed for our 7-segment display rather than the Operates to drive a 7-segment LED display.

OFFTIME accordingly for the clock source.)ī) Read the specification of 74LS47 (BCD-to-7-Segment Decoder shown (Hint: Use the DigClock input from the SOURCE as shown below and (Define the simulation timings for at least one fullĬounting cycle from 0 to 9 and back to 0.) The complete counter circuit by OrCAD and PSPICE. Should be built by a cascaded synchronous binary counter (74LS163) A) Design a single-digit decade counter that counts from 0 to 9 and

0 kommentar(er)

0 kommentar(er)